Overview

This is a follow on course to EE272A. While in EE272A you learn the EDA tool flow and design a pre-specified digital neural network accelerator and an analog block, in EE272B you will leverage your knowledge from EE272A and design and fabricate your own digital/analog/mixed-signal chip! This is a completely project-based course where, working in teams of two, you will propose your own mixed-signal chip, write a Verilog or a synthesizable C++ model of your chip, create a testing/debug strategy for your chip, wrap custom layout to fit into a standard cell system, use synthesis and place and route tools to create the layout of your chip, perform physical verification and finally tape it out in the open-source SkyWater 130 nm technology. Useful for anyone who will build a chip in their research.

Term: 2020-2021 Spring

Units: 3-4

Instructor: Priyanka Raina (praina at stanford dot edu)

TAs: Kartik Prabhu (kprabhu7 at stanford dot edu), Daniel Stanley (dstanley at stanford dot edu)

Lectures: Mon, Wed, 1 - 2:30 PM over Zoom.

Open office hours:

Priyanka: Wed, 2:30 - 3:30 PM over Zoom.

Kartik: Fri, 1 - 2 PM over Zoom.

Daniel: Thu, 1 - 2 PM over Zoom.

Project sync-ups:

Priyanka: Mon, 2:30 - 3 PM (Po-Han/Charles), Mon, 3:30 - 4 PM (John)

Kartik: Mon, 2:30 - 3 PM (Kylee/Sam), Mon, 3:30 - 4 PM (Ismael/George), Tue, 2 - 2:30 PM(Eldrick/Matthew)

Daniel: Tue, 3 - 3:30 PM (Aparna/Weston), Tue, 3:45-4:15 PM (Can/Estelle), Tue, 4:30 - 5 PM (Nikhil)

Canvas: All documents, including lecture notes, and lecture video recordings will be posted on Canvas.

Slack/Piazza: For questions about lectures and project debugging we will use Slack and Piazza. Everyone should also join the skywater-pdk Slack channel for collaborating and debugging with the larger open hardware community.

Pre-requisites

EE271, EE272A and fundamentals of digital/analog circuit design.

Technology and Design Flows

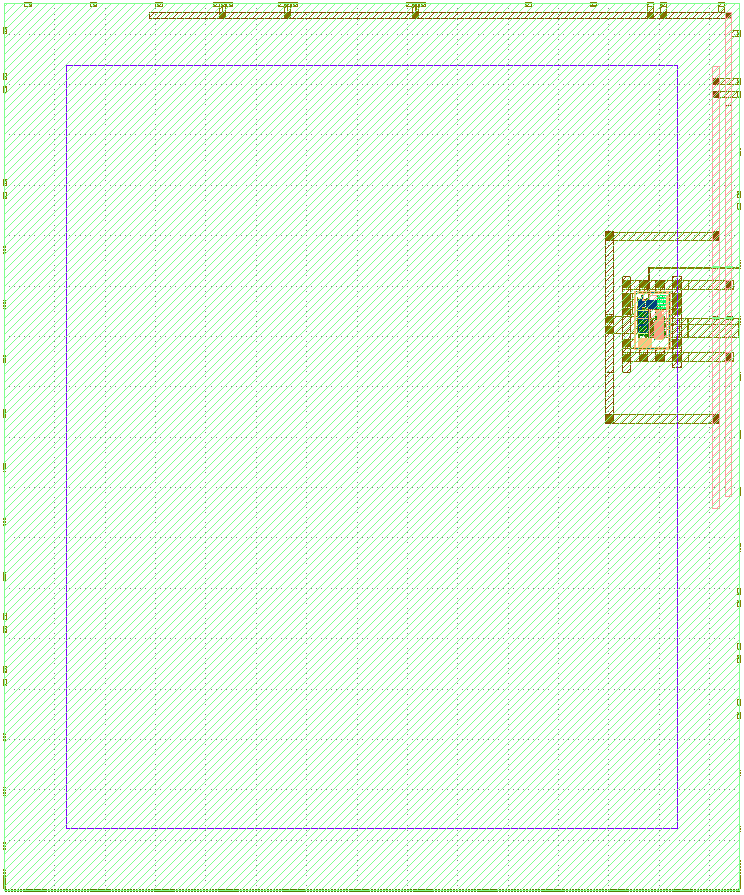

- Technology: SkyWater 130 nm open-source PDK.

- Shuttle: Efabless chipIgnite MPW shuttle, which provides:

- 10 square mm area for the user design per project.

- A standardized harness called caravel with a RISC-V CPU, RAM, and 38 general purpose I/Os.

- 100 packaged ICs and 5 assembled boards post fabrication.

- Analog design flow: We use an open-source analog design flow with the following tools (note that commercial analog design tools like Virtuoso and Calibre are not supported for this open PDK yet):

- PDK files from skywater-pdk, open_pdks and xschem_sky130. All of these are necessary.

- Schematic entry with xschem.

- Simulation with ngspice.

- Layout, extraction and DRC with magic.

- LVS with netgen.

- Manual routing of design using magic into the caravel analog user project. This user project is verified with precheck tool and submitted to the shuttle.

- Digital design flow: We use either an open-source digital design flow called OpenLane, or for advanced features, a (mostly) commercial digital design flow shown below composed using mflowgen. Note that since the open PDK does not have support for Calibre yet, we use a combination of magic and netgen for DRC, extraction and LVS for the digital designs as well. In either case, we perform the final integration of the user design into the caravel user project using OpenLane. This user project is verified with precheck tool and submitted to the shuttle.

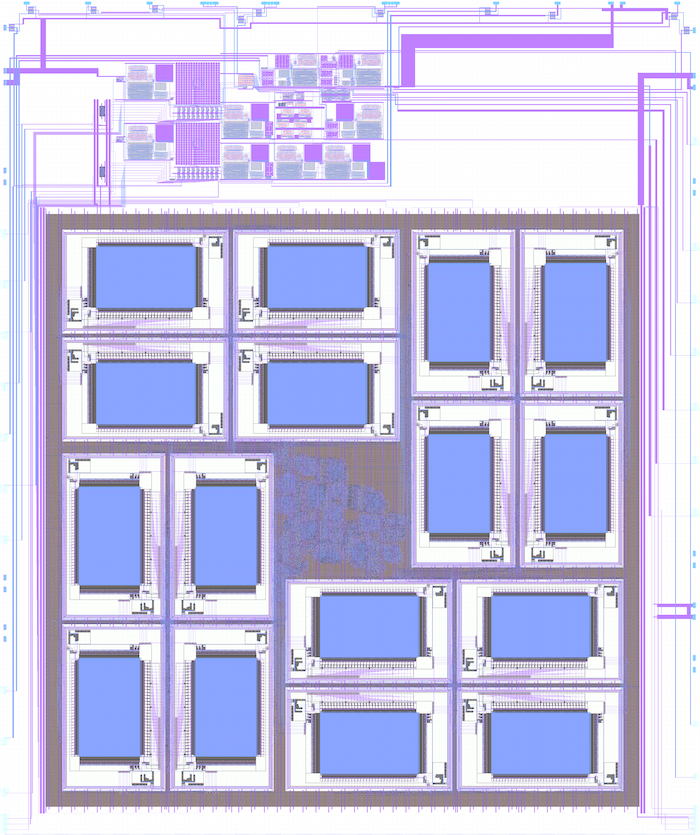

- Memories: For memories, there are two options:

- OpenRAM SRAM compiler: While the support for SkyWater 130 nm technology is still being added to the OpenRAM compiler, there are pre-generated SRAM macros available here. The 1 KByte and 2 KByte macros are verified and can be used in projects. Among the student projects listed below, the RADAR and CGRA projects use OpenRAM SRAM macros.

- DFFRAM compiler: This generates D flip-flop based memories. It is less dense than OpenRAM by a factor of 3, but more dense than what you would get by synthesizing to flip-flops using OpenLane. Among the student projects listed below, CryptoChip and OoO RISC-V projects use DFFRAM.

Resources

Installing Tools

- This video shows how to install ngspice, skywater-pdk, xschem_sky130, and xschem.

- For OpenLane, first install docker, then follow the steps under this quickstart guide.

Documentation

Tutorials and Examples

- Digital flow:

- Our commercial digital design flow composed using mflowgen, with two small examples: a GCD unit and a design with an SRAM.

- OpenLane tutorial.

- Analog flow:

- Caravel:

- Walkthrough of caravel user project and analog user project, and how to submit your design to the shuttle.

- Caravel user project features --- What are the utilities provided by caravel to the user project?

- Aboard caravel --- How to integrate your design with caravel?

- Digital flow:

Talks

- SkywaterPDK: Fully open source manufacturable PDK for a 130nm process by Tim Ansell

- OpenLane, A Digital ASIC Flow for SkyWater 130nm Open PDK by Mohamed Shalan

- The striVe RISC-V SoC Family on SkyWater 130nm by Mohamed Kassem

- Designing new 130nm cells for SkyWater 130nm by James Stine

- OpenRAM on SkyWater 130nm by Matt Guthaus

- Using Magic for DRC checks on SkyWater 130nm by Tim Edwards

- 45 Chips in 30 Days: Open Source ASIC at its best! by Mohamed Kassem

Student Projects

Bandgap Voltage Reference

John Kustin

Documentation: Proposal, Design Review, Final Presentation, Report, Silicon Results

A bandgap reference is a common way to generate a stable voltage with low sensitivities to temperature and supply voltage changes. This project is a CMOS bandgap reference circuit based on the Banba architecture and implemented in SkyWater 130 nm technology. The circuit consists of a self-biased CMOS op-amp, parasitic PNP transistors, resistors, and metal-in-metal (MiM) capacitors. It is designed for a reference voltage of 970.3 mV with an ideal temperature coefficient of 3.6 ppm/°C from 0-70°C. The circuit is open-source and verified to be fully functional in silicon.

OpenPMIC: A Current Mode Buck Converter

Weston Braun, Aparna Tumkur

Documentation: Proposal, Design Review, Final Presentation, Silicon Results

OpenPMIC is a current mode buck converter in SkyWater 130 nm technology designed using a fully open source flow. It also provides a library of power MOS devices for use in future open source designs. This DC-DC converter is designed to convert the 3.3 V I/O voltage to the 1.8 V level required for digital logic and is intended for integration into other projects. The prototype chip achieves a measured power efficiency of 85% at the maximum output power of 720 mW and a peak efficiency of 91% at an output power of 270 mW. This work is the first open-source and silicon-proven PMIC.

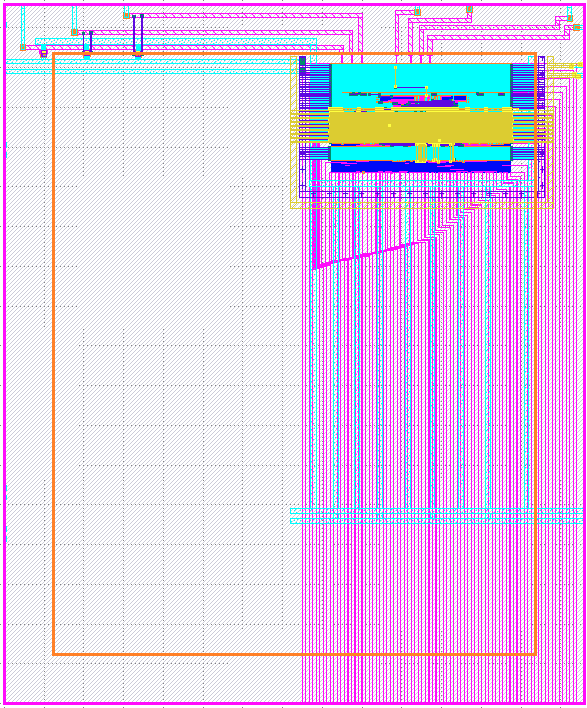

OpenSourcePHY: A High Speed Serial Link

Can Wang, Estelle He

Documentation: Proposal, Design Review, Final Presentation, Silicon Bringup Progress

OpenSourcePHY is an open-source fully synthesizable high speed serial link physical layer (PHY) in SkyWater 130 nm technology, which extends the DragonPHY project. This chip focuses on the transmitter portion of the PHY, which consists of a serializer that aggregates multiple inputs at a relatively low data rate into a single high-speed data output, a driver stage that launches the signal into the physical channel and a clocking circuit that uses a multiplying delay-locked loop (MDLL).

A Mixed-Signal Edge Accelerator for Real-Time mmWave Platform Vibration Compensation

Nikhil Poole

Paper: IEEE Access, Hot Chips 2023

Documentation: Proposal, Design Review, Final Presentation, Silicon Results

This analog/mixed-signal chip is an edge processing unit for real-time vibratory motion compensation in a mmWave radar platform, employing on-chip inertial sensor fusion to deconvolve the effect of parasitic platform micromotions. With its fully analog IMU processing pipeline and digital deconvolution kernel estimator core, the chip generates a complex inverse filter to denoise the incoming radar data, thereby demonstrating a real-time solution for high-fidelity edge-based radar processing.

Wakey-Wakey: A Low-Power, Reconfigurable Wake Word Accelerator

Matthew Pauly, Eldrick Millares

Code: Design, Caravel User Project

Documentation: Proposal, Design Review, Final Presentation, Report, Silicon Bringup Progress

Wakey-Wakey is an acoustic featurization and deep neural network (DNN) accelerator which detects a user-configured wake word in human speech. It interfaces directly with an external microphone and can be configured via a Wishbone bus. Wakey-Wakey's custom DNN architecture and featurization pipeline were co-optimized with its RTL design to minimize area, power, complexity, and latency.

CryptoChip: A RISC-V Processor with Crypto Accelerator

Kylee Krzanich, Sam Xu

Code: Design, Caravel User Project

Documentation: Proposal, Design Review, Final Presentation, Report

In a world where security has become more and more important, this project focuses on designing a crypto-accelerator for a modern RISC-V processor. It achieves 17-66x increase in performance for all cryptographic transactions including but not limited to random number generation and encryption. The accelerator is designed as a tighly-coupled co-processor to a general purpose, RISC-V processor generated using Chipyard.

A RISC-V OoO Processor with Victim Caches

George Klimiashvili, Ismael Garcia

Code: Design, Caravel User Project

Documentation: Proposal, Design Review, Final Presentation

This project designs an out of order (OoO) RISC-V processor based on the BOOM core using the Chipyard framework. The project performs design space exploration of BOOM core parameters to create a design that fits within the caravel user project design constraints. It also explores the benefit of adding a victim cache, which is a small fully-associative cache that holds recently evicted data, to the core.

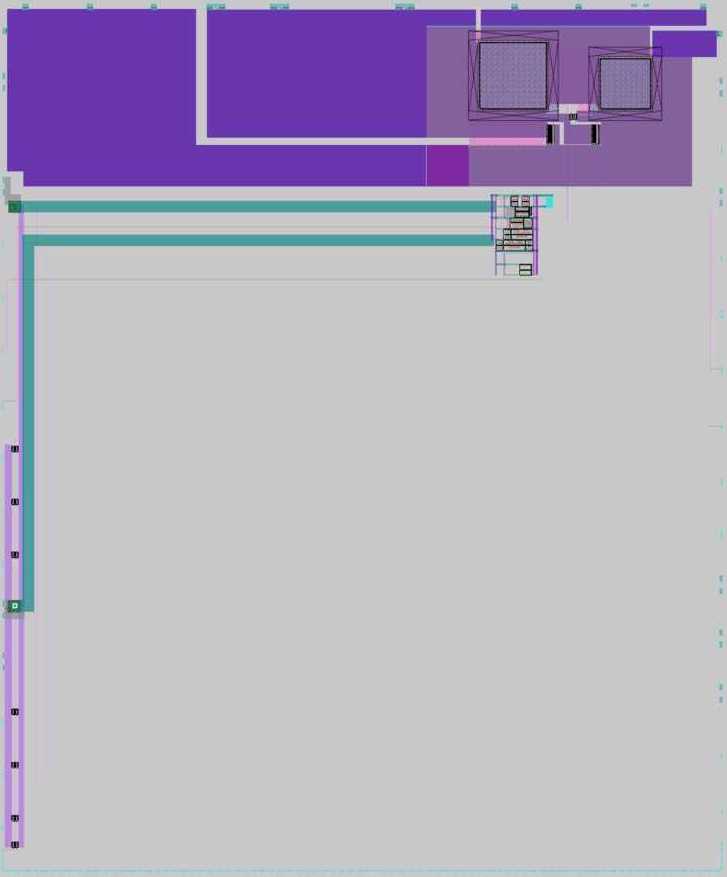

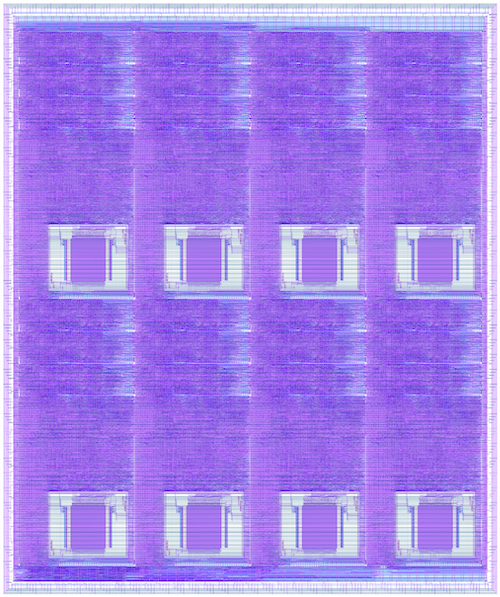

Toy-CGRA: A Coarse-Grained Reconfigurable Array for Flexible Acceleration of Machine Learning and Image Processing

Po-Han Chen, Charles Tsao

Paper: ISCAS 2023

Code: Design, Caravel User Project

Documentation: Proposal, Design Review, Final Presentation, Silicon Bringup Progress

Toy-CGRA is a 4x8 coarse-grained reconfigurable array (CGRA) that enables hardware acceleration of machine learning and image processing applications written in Halide. Compared to an FPGA, it provides faster configuration time and lower power consumption. Compared to an ASIC, it has higher flexibility. Toy-CGRA runs at 66 MHz and occupies an area of 3.5 mm x 2.9 mm.

Course Schedule

| Week | Date | Topic | Presenter |

|---|---|---|---|

| 1 | Mon, Mar 29 | Lecture: Class overview, updates to digital and analog flows | Priyanka |

| 1 | Wed, Mar 31 | Lecture: Project overview presentations (10 minutes per group) | All groups |

| 2 | Mon, Apr 5 | Lecture: Analog validation | Daniel |

| 2 | Wed, Apr 7 | Lecture: OpenLane flow, generating hard macro from design (analog and digital) | Priyanka |

| 3 | Mon, Apr 12 | Lecture: Caravel integration tutorial | Kartik |

| 3 | Wed, Apr 14 | Lecture: Magic tutorial | Daniel |

| 4 | Mon, Apr 19 | Lecture: Caravel I/Os | Priyanka |

| 4 | Wed, Apr 21 | Lecture: Fixture tutorial | Daniel |

| 5 | Mon, Apr 26 | Lecture: Mid-quarter design review, functional demo (40 + 40 minutes) | Nikhil, Weston/Aparna |

| 5 | Wed, Apr 28 | Lecture: Mid-quarter design review, functional demo (40 + 40 minutes) | Estelle/Can, John |

| 5 | Fri, Apr 30 | RTL/schematics + tests due | |

| 6 | Mon, May 3 | Lecture: Mid-quarter design review, functional demo (40 + 40 minutes) | George/Ismael, Kylee/Sam |

| 6 | Wed, May 5 | Lecture: Mid-quarter design review, functional demo (40 + 40 minutes) | Eldrick/Matthew, Charles/Po-Han |

| 7 | Mon, May 10 | Debugging help | Priyanka |

| 7 | Wed, May 12 | Q&A with Efabless | |

| 8 | Mon, May 17 | Debugging help | |

| 8 | Wed, May 19 | Debugging help | |

| 8 | Fri, May 21 | Inital layout due | |

| 9 | Mon, May 24 | Debugging help | |

| 9 | Wed, May 26 | Lecture: Final presentation in class (20 minutes per group) | Eldrick/Matthew, Kylee/Sam, George/Ismael, Charles/Po-Han |

| 10 | Mon, May 31 | Memorial Day (holiday, no classes) | |

| 10 | Wed, Jun 2 | Lecture: Final presentation in class (20 minutes per group) | Estelle/Can, Nikhil, John, Weston/Aparna |

| 10 | Fri, Jun 4 | Tapeout --- Submit designs to shuttle |

Grading

| Component | Weight |

|---|---|

| Project overview presentation | 5% |

| RTL/schematic + tests | 20% |

| Mid-quarter design review | 15% |

| Layout + signoff | 20% |

| Final presentation | 15% |

| Final report (Only if taking the class for 4 units) | 15% |

| Weekly syncups | 10% |