Overview

In EE372 you will leverage your knowledge of chip design flows from EE272 and design and fabricate your own digital/analog/mixed-signal chip! This is a completely project-based course where, working in teams of two, you will propose an idea for your own chip, write a Verilog or a synthesizable C++ model or a schematic of your chip, verify it extensively, generate a layout of your chip either manually or using synthesis and place and route tools, perform physical verification and finally tape it out in the open-source SkyWater 130 nm technology. This course is useful for anyone who is thinking about designing a chip in their research or in their careers after graduation.

Technology and Design Flows

- Technology: SkyWater 130 nm open-source PDK.

- Shuttle: Efabless chipIgnite MPW shuttle, which provides:

- 10 square mm area for the user design per project.

- A standardized harness called caravel with a RISC-V CPU, RAM, and 38 general purpose I/Os.

- 100 packaged ICs and 5 assembled boards post fabrication.

- Analog design flow: We use an open-source analog design flow with the following tools (note that commercial analog design tools like Virtuoso and Calibre are not supported for this open PDK yet):

- PDK files from skywater-pdk, open_pdks and xschem_sky130. All of these are necessary.

- Schematic entry with xschem.

- Simulation with ngspice.

- Layout, extraction and DRC with magic.

- LVS with netgen.

- Manual routing of design using magic into the caravel analog user project. This user project is verified with precheck tool and submitted to the shuttle.

- Digital design flow: We use either an open-source digital design flow called OpenLane, or for advanced features, a (mostly) commercial digital design flow shown below composed using mflowgen. Note that since the open PDK does not have support for Calibre yet, we use a combination of magic and netgen for DRC, extraction and LVS for the digital designs as well. In either case, we perform the final integration of the user design into the caravel user project using OpenLane. This user project is verified with precheck tool and submitted to the shuttle.

- Memories: For memories, there are two options:

- OpenRAM SRAM compiler: While the support for SkyWater 130 nm technology is still being added to the OpenRAM compiler, there are pre-generated SRAM macros available here. The 1 KByte and 2 KByte macros are verified and can be used in projects.

- DFFRAM compiler: This generates D flip-flop based memories. It is less dense than OpenRAM by a factor of 3, but more dense than what you would get by synthesizing to flip-flops using OpenLane.

Resources

Installing Tools

- This video shows how to install ngspice, skywater-pdk, xschem_sky130, and xschem.

- For OpenLane, first install docker, then follow the steps under this quickstart guide.

Documentation

Tutorials and Examples

- Digital flow:

- Our commercial digital design flow composed using mflowgen, with two small examples: a GCD unit and a design with an SRAM.

- OpenLane tutorial.

- Analog flow:

- Caravel:

- Walkthrough of caravel user project and analog user project, and how to submit your design to the shuttle.

- Caravel user project features --- What are the utilities provided by caravel to the user project?

- Aboard caravel --- How to integrate your design with caravel?

- Digital flow:

Talks

- 2022 Free Silicon Conference (FSiC) Talk Videos

- SkywaterPDK: Fully open source manufacturable PDK for a 130nm process by Tim Ansell

- OpenLane, A Digital ASIC Flow for SkyWater 130nm Open PDK by Mohamed Shalan

- The striVe RISC-V SoC Family on SkyWater 130nm by Mohamed Kassem

- Designing new 130nm cells for SkyWater 130nm by James Stine

- OpenRAM on SkyWater 130nm by Matt Guthaus

- Using Magic for DRC checks on SkyWater 130nm by Tim Edwards

- 45 Chips in 30 Days: Open Source ASIC at its best! by Mohamed Kassem

Student Projects

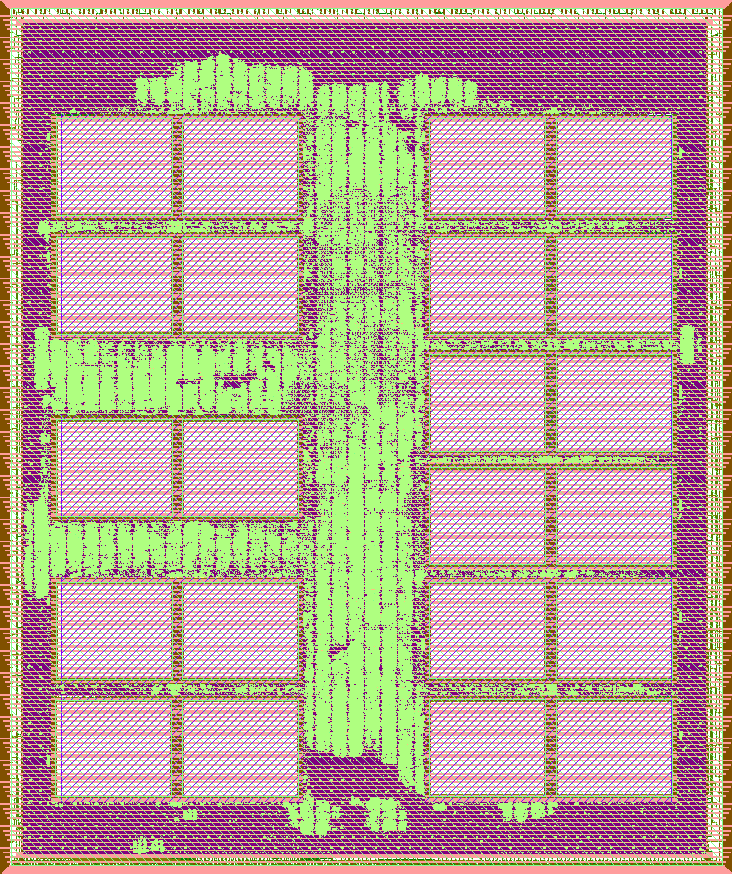

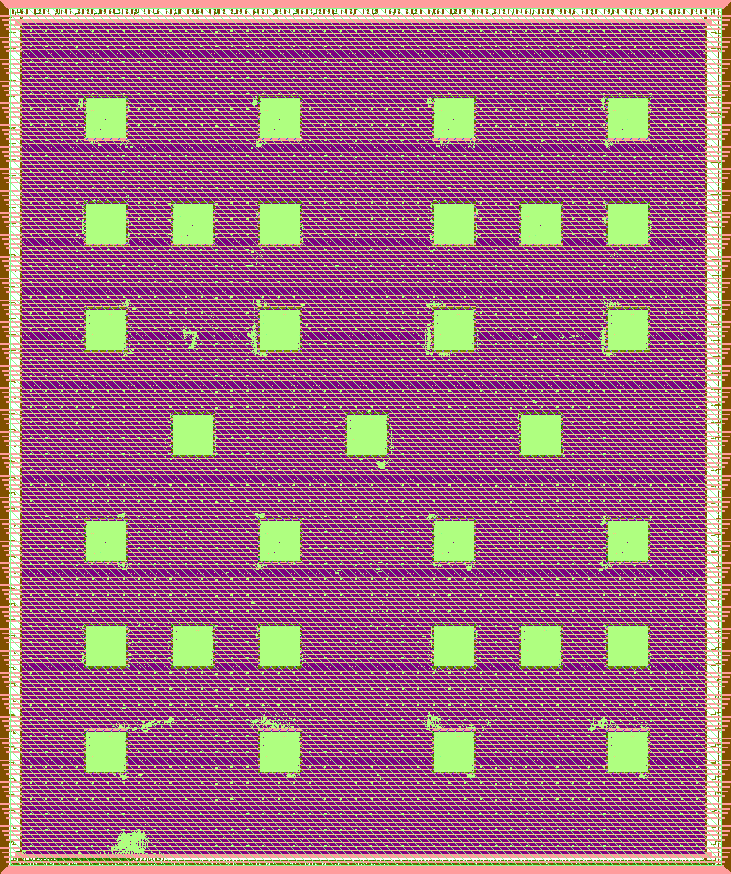

Fast ANN Fieldious: An Approximate Nearest-Neighbor (ANN) Field Hardware Accelerator

Chris Calloway, Jake Ke

Code: Design, Caravel User Project

Documentation: Proposal, Design Review, Final Presentation, Report

Fast ANN Fieldious is a hardware accelerator for computing approximate nearest neighbor fields (ANNF). This is an important but computationally expensive calculation needed for computer vision tasks such as optical flow, video compression and image pattern matching. Our accelerator implements a parallelized and pipelined version of the propagation assisted K-D tree algorithm for computing ANNF. The design runs at a clock frequency of 150 MHz, and achieves a throughput of 5.74M vectors/seconds with a power consumption of 204 mW.

OpenPUF: A Bistable Ring Physical Unclonable Function

Luke Sammarone, Xiaolin Wu

Documentation: Proposal, Design Review, Final Presentation, Report

Physical unclonable functions (PUFs) contain cryptographic secrets not in the form of digital values stored in memory, but in the physical characteristics of the hardware itself, enabling authentication and secret key generation securely and energy efficiently. This chip features four instances of 32-bit, 64-bit, and 128-bit bistable ring PUFs for characterization of stability, uniqueness, and settling time. The PUF super block occuies an area of 1.02 square mm and shows 48% uniqueness in post-layout simulation.

Kairos: A Vector Processor for Error-State Extended Kalman Filter Acceleration

Jeffery Yu, Yuchen Mei

Code: Design, Caravel User Project

Documentation: Proposal, Design Review, Final Presentation, Report

Kairos is a SIMD single precision floating point vector processor, with instructions conforming to the RISC-V ISA. It implements operations such as vector fused multipy-add, matrix inversion, and matrix multiply-add, to efficiently accelerate error-state extended Kalman filter (ES-EKF) for trajectory estimation.

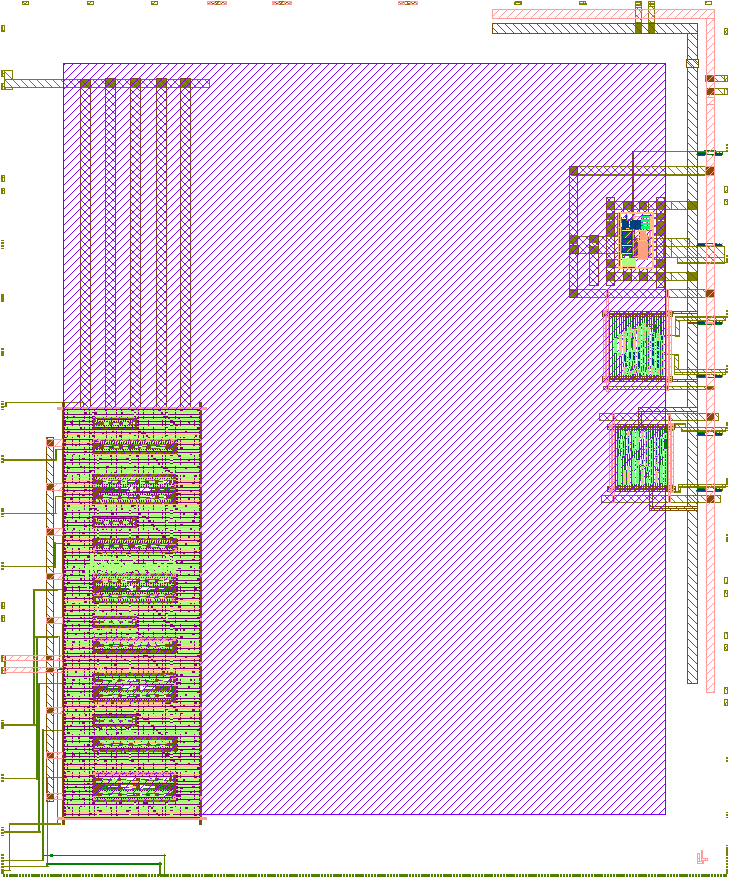

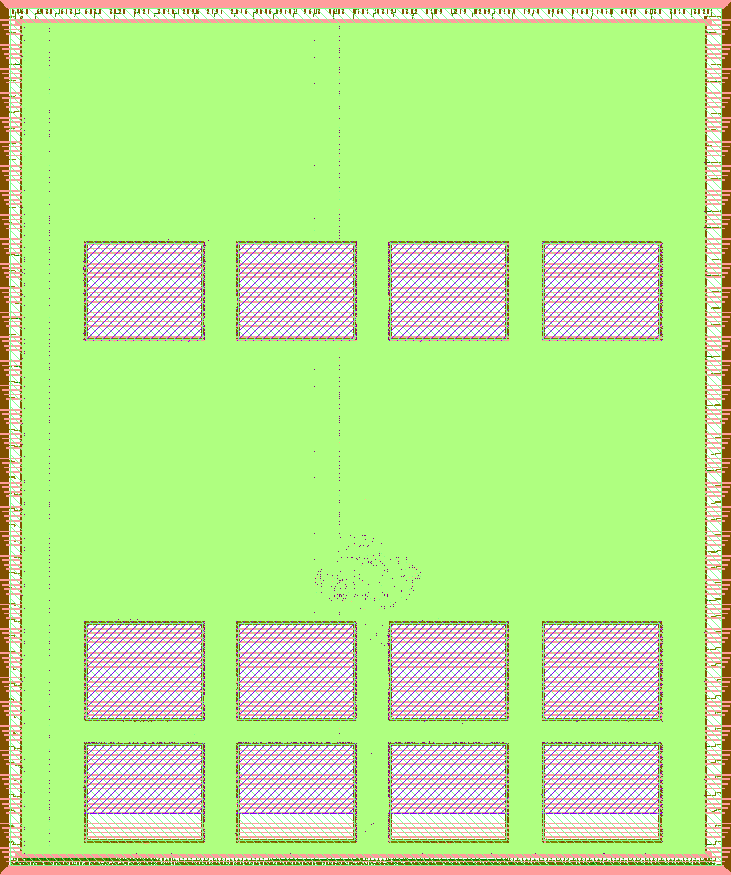

12-bit 10-KSPS Incremental Delta-Sigma ADC in Skywater 130 nm

Raymond Yang, Yaqing Xia

Paper: IEEE Design & Test

Documentation: Proposal, Design Review, Final Presentation, Report

This project is a 12-bit 10 KSPS incremental delta-sigma analog-to-digital converter (ADC) designed for sensor interface and instrumentation applications. The ADC consists of a second-order incremental modulator and three post-integrators. The total area of the ADC is 0.55 square mm, with 0.53 square mm for analog modulator and 0.02 square mm for digital filter.

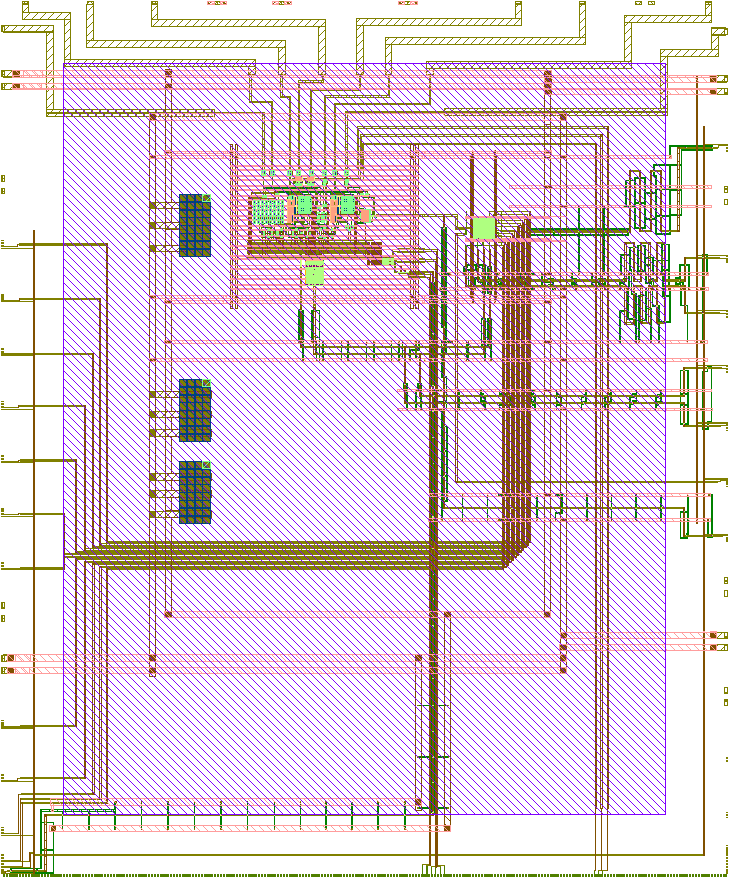

Grapevine: An Asynchronous Numerical Classifier Using Sparse Grids

Leo Liu, Priyanka Dilip

Code: Design, Caravel User Project

Documentation: Proposal, Design Review, Final Presentation

Grid-based numerical methods sample N-dimensional functions at regular intervals to produce an N-dimensional set of discrete “grid points”. By breaking up grid points into hierarchical subgrids and eliminating subgrids above a certain hierarchy, one can obtain a sparsified grid space that reduces computational complexity. Grapevine is a hardware accelerator for solving classification problems using the sparse grid approach. It supports up to 6 dimensions and 256 grid points. Each grid point is implemented using a single processing element (PE). An asynchronous network-on-a-chip overlays the PEs to provide low-latency multicast routing.

Automated Analog Layout of Bandgap Reference Circuit

Yueting Li, Xingyu Ni

Documentation: Proposal, Design Review, Final Presentation, Report

This project ports an automatic analog layout generation tool called aloe to work with SkyWater 130 nm technology. Aloe uses a digital place and route tool together with a genetic algorithm to meet different analog layout specifications. Using this tool, we generated several layouts for a bandgap voltage reference circuit on this chip, and we will compare these with a manually laid out version from the previous offering of this course.

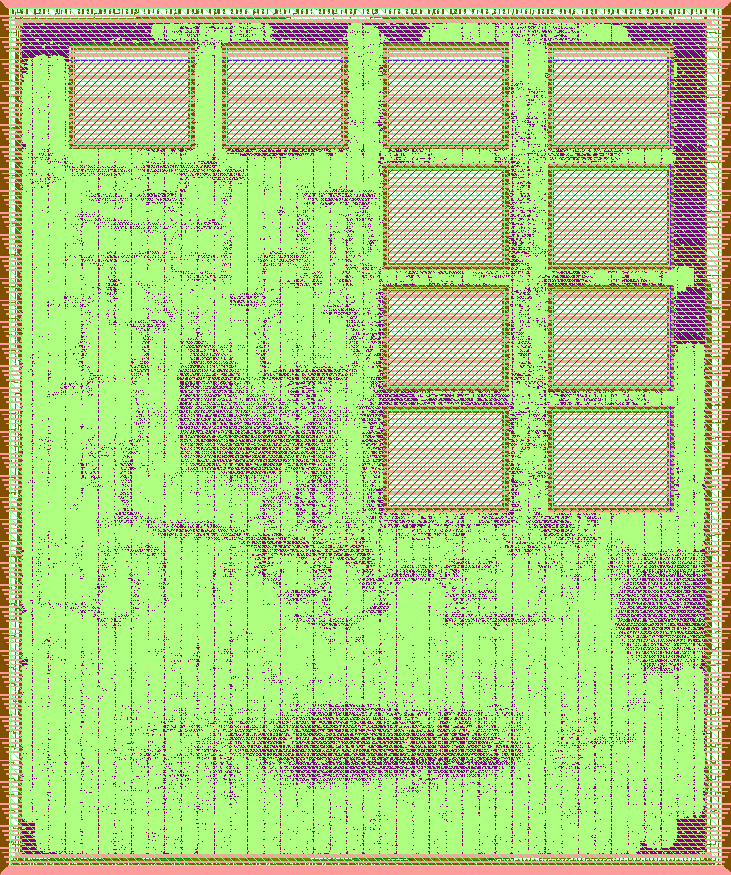

OpenEnclave: A Basic BGV Homomorphic Encryption Accelerator

Ian MacFarlane, JD Kelly

Code: Design, Caravel User Project

Documentation: Proposal, Design Review, Final Presentation, Report

Homomorphic encryption is a promising technique to enable secure computation on sensitive data. It has particualy seen significant interest for use in cloud based machine learning. OpenEnclave is an open-source hardware accelerator for the BGV fully homomorphic encryption scheme in SkyWater 130 nm technology. The design is capable of operating at 50 MHz and is comparable to or outperforms existing FPGA implementations in the literature.

Logistics

Term: 2021-2022 Spring

Units: 3-5

For 3 units - Create a design all the way to clean layout, but no integration into carrier SoC, and no tapeout. Deliverables will be design's code repository with working tests and documentation.

For 4 units - Everything for 3 units + integration into carrier SoC + tapeout.

For 5 units - Everything for 4 units + VLSI-style final paper with circuit description, simulation results and comparison with related work.

Instructor: Priyanka Raina (praina at stanford dot edu)

TAs: Can Wang, Charles Tsao

Lectures: Tue, Thu 9:45 - 11:15 AM at Hewlett Teaching Center 102.

Open office hours:

Priyanka Raina: Thu 11:15 - 12:15 in Allen 114.

Charles Tsao: Fri 10 - 11 in Packard 104.

Can Wang: Tue 11:15 - 12:15 in Packard 104.

Project sync-ups:

Priyanka Raina: Tue 11:30 - 12 (Chris Calloway & Jake Ke), Tue 12 - 12:30 (Jeffery Yu & Yuchen Mei) in Allen 114.

Charles Tsao: Wed 1 - 1:30 (Ian MacFarlane & JD Kelly), Wed 2 - 2:30 (Leo Liu & Priyanka Dilip) in Packard 109.

Can Wang: Wed 12:00 - 12:30 (Yueting Li & Xingyu Ni), Thu 11:15 - 11:45 (Luke Sammarone & Xiaolin Wu), Thu 4:00 - 4:40 (Raymond Yang & Yaqing Xia).

Canvas: All documents, including lecture notes, and lecture video recordings will be posted on Canvas.

Slack/Piazza: For questions about lectures and project debugging we will use Slack and Ed Discussion. Everyone should also join the skywater-pdk Slack channel for collaborating and debugging with the larger open hardware community.

Pre-requisites

EE271, EE272 and fundamentals of digital/analog circuit design.

Course Schedule

| Week | Date | Topic | Presenter |

|---|---|---|---|

| 1 | Tue, Mar 29 | Lecture: Tapeout process overview, digital and analog flows | Priyanka Raina |

| 1 | Thu, Mar 31 | Lecture: Project overview presentations (10 minutes per group) | All groups |

| 2 | Tue, Apr 5 | Lecture: Caravel SoC | Priyanka Raina |

| 2 | Thu, Apr 7 | Lecture: Digital flow post innovus signoff and analog flow considerations | Priyanka Raina |

| 3 | Tue, Apr 12 | Lecture: Caravel integration, simulation, and OpenLane tutorial | Charles Tsao |

| 3 | Thu, Apr 14 | Lecture: Analog validation | Can Wang |

| 4 | Tue, Apr 19 | Lecture: Integrating user design in caravel - I | Priyanka Raina |

| 4 | Thu, Apr 21 | Debugging help | Priyanka Raina |

| 5 | Tue, Apr 26 | Lecture: Mid-quarter design review, functional demo (30 minutes per group) | Chris Calloway/Jake Ke, Ian MacFarlane/JD Kelly |

| 5 | Thu, Apr 28 | Lecture: Mid-quarter design review, functional demo (30 minutes per group) | Raymond Yang/Yaqing Xia, Luke Sammarone/Xiaolin Wu, Yueting Li/Xingyu Ni |

| 5 | Sat, Apr 30 | RTL/schematics + tests due | |

| 6 | Tue, May 3 | Lecture: Mid-quarter design review, functional demo (30 minutes per group) | Jeffery Yu/Yuchen Mei, Leo Liu/Priyanka Dilip |

| 6 | Thu, May 5 | Lecture: Integrating user design in caravel - II | Can Wang |

| 7 | Tue, May 10 | Lecture: Virtuoso tutorial and how to generate timing models | Priyanka Raina |

| 7 | Thu, May 12 | Debugging help | Priyanka Raina |

| 8 | Tue, May 17 | Lecture: Integrating user design in caravel - III | Priyanka Raina |

| 8 | Thu, May 19 | Running static timing analysis on caravel SoC | Priyanka Raina |

| 9 | Mon, May 23 | Inital layout due | |

| 9 | Tue, May 24 | Lecture: Final presentation in class (30 minutes per group) | Jeffery Yu/Yuchen Mei, Leo Liu/Priyanka Dilip |

| 9 | Thu, May 26 | Lecture: Final presentation in class (30 minutes per group) | Raymond Yang/Yaqing Xia, Luke Sammarone/Xiaolin Wu, Yueting Li/Xingyu Ni |

| 10 | Tue, May 31 | Lecture: Final presentation in class (30 minutes per group) | Chris Calloway/Jake Ke, Ian MacFarlane/JD Kelly |

| 10 | Wed, Jun 8 | Tapeout --- Submit designs to shuttle |

Grading

| Component | Weight |

|---|---|

| Project overview presentation | 5% |

| RTL/schematic + tests | 20% |

| Mid-quarter design review | 15% |

| Layout + signoff | 20% |

| Final presentation | 15% |

| Final report (Only if taking the class for 4 units) | 15% |

| Weekly syncups | 10% |